Introduction to IBM® Power® Reliability, Availability, and Serviceability for Power10 processor-based systems using IBM PowerVM®

IBM Infrastructure Daniel Henderson, Irving Baysah Updated December 2024

### Trademarks, Copyrights, Notices and Acknowledgements

#### **Trademarks**

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corporation in the United States, other countries, or both. These and other IBM trademarked terms are marked on their first occurrence in this information with the appropriate symbol (® or TM), indicating US registered or common law trademarks owned by IBM at the time this information was published. Such trademarks may also be registered or common law trademarks in other countries. A current list of IBM trademarks is available on the Web at http://www.ibm.com/legal/copytrade.shtml

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

| Active<br>Memory <sup>™</sup> | AIX®      | Power®                  | Power<br>Hypervisor <sup>™</sup> |                                   |                                  |

|-------------------------------|-----------|-------------------------|----------------------------------|-----------------------------------|----------------------------------|

| Power®<br>Power®<br>Power6®   | Power7®   | Power7+ <sup>™</sup> Po | wer8®                            | Power®<br>PowerHA®                | PowerLinux <sup>TM</sup>         |

| PowerVM <sup>®</sup>          | System x® | System z®               | PowerVC                          | Power<br>Hypervisor <sup>TM</sup> | Power Architecture <sup>TM</sup> |

| IBM®                          |           |                         |                                  |                                   |                                  |

Additional Trademarks may be identified in the body of this document.

Google is a registered trademark of Google LCC. Intel is a registered trademark of the Intel corporation.

Other company, product, or service names may be trademarks or service marks of others.

#### **Notices**

The last page of this document contains copyright information, important notices, and other information.

#### **Acknowledgements**

While this whitepaper has two principal authors/editors it is the culmination of the work of a number of different subject matter experts within IBM who contributed ideas, detailed technical information, and the occasional photograph and section of description.

These include the following:

Kanisha Patel, Kevin Reilly, Marc Gollub, Julissa Villarreal, Michael Mueller, George Ahrens, Kanwal Bahri, Steven Gold, Jim O'Connor, K Paul Muller, Ravi A. Shankar, Kevin Reick, Peter Heyrman, Dave Stanton, Dan Hurlimann, Kaveh Naderi, Nicole Nett, John Folkerts and Hoa Nguyen.

# **Table of Contents**

| Trademarks, Copyrights, Notices and Acknowledgements                           | 2  |

|--------------------------------------------------------------------------------|----|

| Trademarks                                                                     |    |

| Notices                                                                        |    |

| Acknowledgements                                                               |    |

| Table of Contents                                                              | 3  |

| Introduction                                                                   | 7  |

| Section 1: Overview of Power10 Processor-based systems                         | 8  |

| Comparative Discussion                                                         |    |

| Figure 1: Power9/Power10 Servers RAS Highlights Comparison                     |    |

| Figure 2: Power10 Servers RAS Highlights Comparison                            |    |

| IBM Power E1080                                                                |    |

| System Structure                                                               |    |

| Figure 3: Power E1080 Structure Simplified View                                |    |

| Power E1080 Processor RAS                                                      |    |

| Power E1080 Memory Subsystem                                                   |    |

| Figure 4: DDIMM Memory Features                                                |    |

| Buffer                                                                         |    |

| OMI                                                                            |    |

| Memory ECC                                                                     | 14 |

| Dynamic Row Repair                                                             |    |

| Spare Temperature Sensors                                                      | 14 |

| Unique to 4U DDIMM: Spare DRAMs                                                | 14 |

| Power Management                                                               | 14 |

| Power E1080 SMP Interconnections                                               | 15 |

| Power E1080 Processor to Processor SMP Fabric Interconnect Within a CEC Drawer | 15 |

| Power E1080 CEC Drawer to CEC Drawer SMP Fabric Interconnect Design            | 15 |

| Figure 5: SMP Fabric Bus Slice                                                 | 16 |

| Figure 6: Time Domain Reflectometry                                            |    |

| Power E1080 SMP Fabric Interconnect Design within a CEC Drawer                 | 17 |

| Internal I/O                                                                   | 18 |

| Power E1080 and E980 Telemetry Data                                            | 18 |

| IBM Power E1050                                                                | 19 |

| System Structure                                                               | 19 |

| Figure 7: Power E1050 Structure Simplified View                                | 20 |

| Power E1050 Processor RAS                                                      | 20 |

| Power E1050 Memory RAS                                                         |    |

| Figure 8: E950 DIMM vs E1050 DDIMM RAS Comparison                              |    |

| Power E1050 I/O RAS                                                            |    |

| Figure 9: Power E1050 I/O Slot Assignments                                     |    |

| DASD Options                                                                   |    |

| Power F1050 Service Processor                                                  | 22 |

| IBM Power S1014, S1022, S1024 Servers                                                                             |    |

|-------------------------------------------------------------------------------------------------------------------|----|

| System Structure                                                                                                  |    |

| Figure 10: Power S1024 Structure Simplified View                                                                  |    |

| Figure 11: Power S1024 Structure Simplified View With eSCM                                                        |    |

| Power S1014, S1022, S1024 Processor and Memory RAS                                                                |    |

| Figure 12: S9xx ISDIMM vs 2U DDIMM RAS Comparison                                                                 |    |

| Power S1014, S1022, S1024 I/O RAS                                                                                 |    |

| Figure 13: Power S1024 I/O Slot Assignments                                                                       |    |

| DASD Options                                                                                                      |    |

| Power S1014, S1022, S1024 Service Processor                                                                       |    |

| IBM Power S1012                                                                                                   |    |

| NVMe Expansion Drawer (NED24)                                                                                     |    |

| Figure 14: The NED24 I/O Subsystem Structure                                                                      |    |

| Figure 15: NVMe Expansion Drawer RAS Feature Matrix                                                               |    |

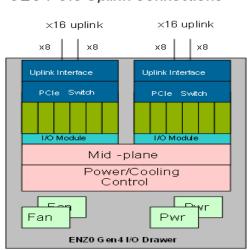

| ENZ0 PCle Gen4 I/O Expansion Drawer                                                                               |    |

| Figure 16: ENZ0 PCIe Gen4 I/O Expansion Drawer                                                                    |    |

| Figure 17: ENZ0 PCIe Gen4 I/O Expansion Drawer RAS Features                                                       | 32 |

| Section 2: General RAS Philosophy and Architecture                                                                | 33 |

| Philosophy                                                                                                        | 33 |

| Integrate System Design                                                                                           | 33 |

| Figure 18: IBM Enterprise System Stacks (Power8 Design Point)                                                     | 34 |

| Incorporate Experience                                                                                            |    |

| Architect for Error Reporting and Fault Isolation                                                                 |    |

| Leverage Technology and Design for Soft Error Management                                                          |    |

| Deploy Strategic Spare Capacity to Self-Heal Hardware                                                             |    |

| Redundant Definition                                                                                              |    |

| Spare Definition                                                                                                  |    |

| Focus on OS Independence                                                                                          |    |

| Build System Level RAS Rather Than Just Processor and Memory RAS                                                  |    |

| Error Reporting and Handling                                                                                      |    |

| First Failure Data Capture Architecture                                                                           |    |

| Figure 19: Handled Errors Classified by Severity and Service Actions Required                                     |    |

| First Failure Data Capture Analysis (Processor Runtime Diagnostics)                                               |    |

| Periodic Processor Exerciser/Diagnostics Program (Runtime Processor Diagnostics) PowerVM Partitioning and Outages |    |

| Section 3: Power10 Subsystems RAS Details                                                                         |    |

| Processor RAS Details                                                                                             |    |

| Figure 20: Power6 Processor Design Compared to Power10                                                            | _  |

| Hierarchy of Error Avoidance and Handling                                                                         |    |

| Figure 21: Error Handling Methods Highlights                                                                      |    |

| Processor Module Design and Test                                                                                  |    |

| Memory RAS Details                                                                                                | 48 |

| Memory Hierarchy of Error Avoidance and Handling                                                                  |    |

| Figure 22: Error Handling Methods Highlights                                                                      |    |

| Memory RAS Beyond ECC                                                                                             |    |

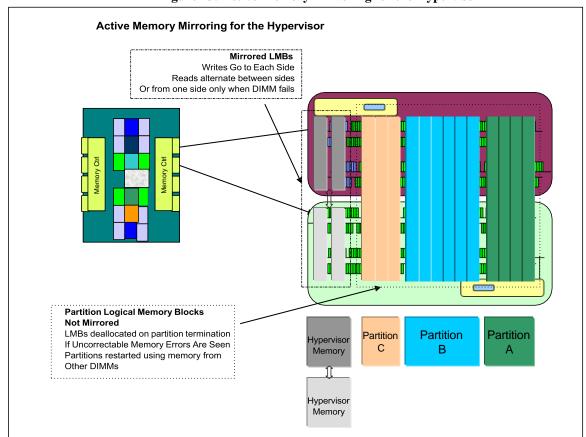

| Hypervisor Memory Mirroring                                                                                       |    |

| Figure 23: Active Memory Mirroring for the Hypervisor                 | 50         |

|-----------------------------------------------------------------------|------------|

| Dynamic Deallocation/Memory Substitution                              | 50         |

| RAS beyond Processors and Memory                                      | 51         |

| Introduction                                                          |            |

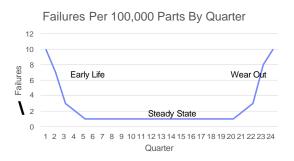

| Serial Failures, Load Capacity and Wear-out                           | 51         |

| Common Mode Failures                                                  |            |

| Fault Detection/Isolation and Firmware and Other Limitations          | 53         |

| Power and Cooling Redundancy Details                                  | 53         |

| Power Supply Redundancy                                               | 5 <i>3</i> |

| Voltage Regulation                                                    | 54         |

| Redundant Clocks                                                      | 55         |

| Service Processor and Boot Infrastructure                             | 55         |

| Trusted Platform Module (TPM)                                         | 56         |

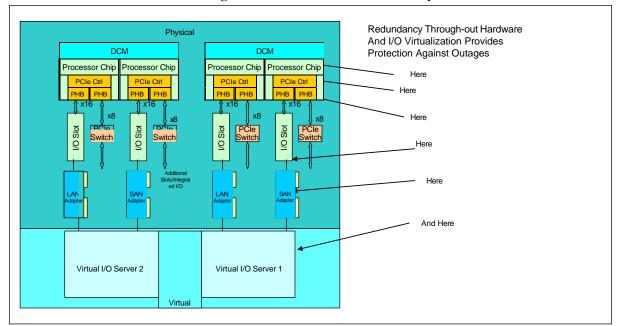

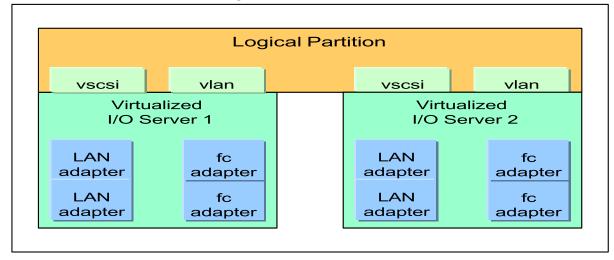

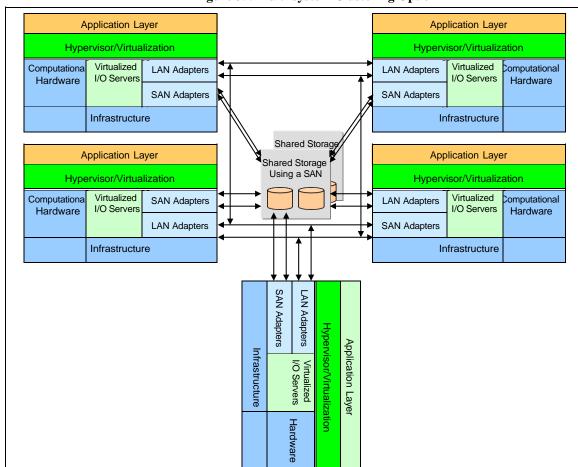

| I/O Subsystem and VIOS <sup>TM</sup>                                  | 56         |

| Figure 24: End-to-End I/O Redundancy                                  | 57         |

| PCIe Gen4 Expansion Drawer Redundancy                                 | 57         |

| Figure 25: Maximum Availability with Attached I/O Drawers             | 58         |

| Planned Outages                                                       | 58         |

| Updating Software Layers                                              | 59         |

| Concurrent Repair                                                     | 59         |

| Integrated Sparing                                                    | 59         |

| Clustering and Cloud Support                                          | 60         |

| PowerHA SystemMirror                                                  |            |

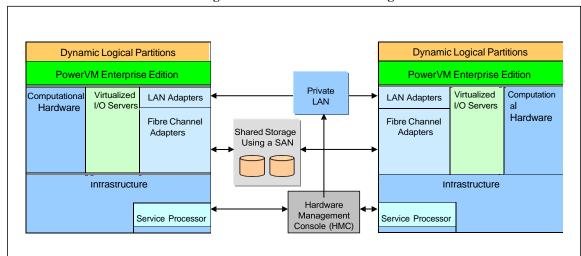

| Live Partition Mobility                                               |            |

| Figure 26: LPM Minimum Configuration                                  |            |

| Minimum Configuration                                                 |            |

| Figure 27: I/O Infrastructure Redundancy                              | 62         |

| Figure 28: Use of Redundant VIOS                                      | 62         |

| PowerVC <sup>TM</sup> and Simplified Remote Restart                   |            |

| Error Detection in a Failover Environment                             | 63         |

| Castian 4. Daliability and Availability in the Data Contan            |            |

| Section 4: Reliability and Availability in the Data Center            |            |

| The R, A and S of RAS                                                 | 64         |

| Introduction                                                          |            |

| RAS Defined                                                           |            |

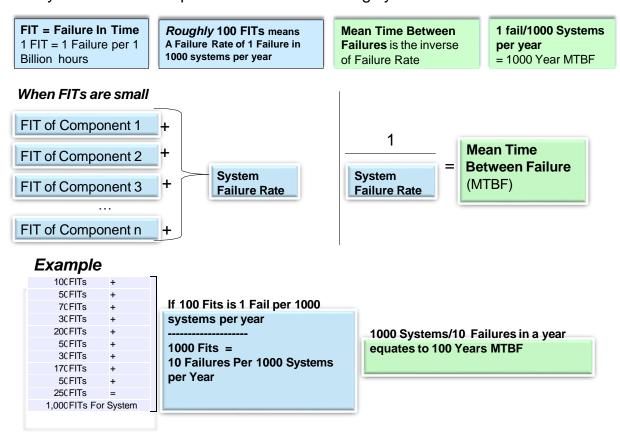

| Reliability Modeling.                                                 |            |

| Figure 29: Rough Reliability Cheat Sheet*                             |            |

| Different Levels of Reliability                                       |            |

| Costs and Reliability                                                 |            |

| End User Costs                                                        |            |

|                                                                       |            |

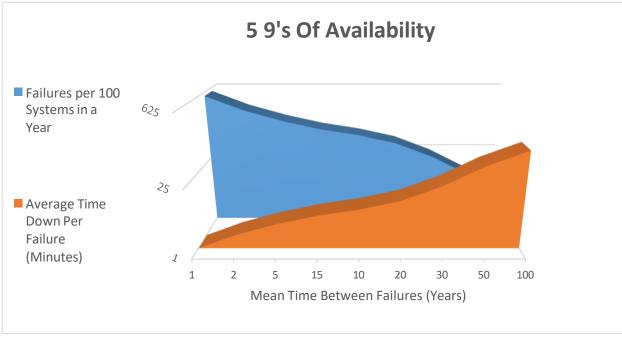

| Measuring Availability                                                |            |

| Figure 30: Different MTBFs but same 5 9's of availability             |            |

| Contributions of Each Element in the Application Stack                |            |

| Figure 31: Hypothetical Standalone System Availability Considerations |            |

| Critical Application Simplification                                   |            |

| Measuring Application Availability in a Clustered Environment         |            |

| Figure 32: Ideal Clustering with Enterprise-Class Hardware Example    | 71<br>70   |

| i ignie 52. idea Cinsternig win Linerprise-Ciuss Huraware Example     | / 4        |

| Recovery Time Caution                                                         | 72 |

|-------------------------------------------------------------------------------|----|

| Clustering Infrastructure Impact on Availability                              | 72 |

| Real World Fail-over Effectiveness Calculations                               | 73 |

| Figure 33: More Realistic Model of Clustering with Enterprise-Class Hardware. | 74 |

| Figure 34: More Realistic Clustering with Non-Enterprise-Class Hardware       | 75 |

| Reducing the Impact of Planned Downtime in a Clustered Environment            | 75 |

| HA Solutions Cost and Hardware Suitability                                    | 76 |

| Clustering Resources                                                          | 76 |

| Figure 35: Multi-system Clustering Option                                     | 77 |

| Using High Performance Systems                                                |    |

| Cloud Service Level Agreements and Availability                               |    |

| Figure 36: Hypothetical Service Level Agreement                               |    |

| Figure 37: Hypothetical Application Downtime meeting a 99.99% SLA             |    |

| Section 5: Serviceability                                                     | 80 |

| Service Environment                                                           |    |

| Service Interface                                                             |    |

| First Failure Data Capture and Error Data Analysis                            |    |

| Diagnostics                                                                   |    |

| Automated Diagnostics                                                         |    |

| Stand-alone Diagnostics                                                       |    |

| Concurrent Maintenance                                                        |    |

| Service Labels                                                                | 82 |

| QR Labels                                                                     |    |

| Packaging for Service                                                         |    |

| Error Handling and Reporting                                                  |    |

| Service Action Alert                                                          | 83 |

| Call Home                                                                     | 83 |

| IBM Electronic Services                                                       | 84 |

| Benefits of ESA                                                               | 84 |

| Remote Code Load (RCL)                                                        | 85 |

| Client Support Portal                                                         | 85 |

| Summary                                                                       | 86 |

| Investing in RAS                                                              |    |

| Final Word                                                                    |    |

| About the principal authors/editors:                                          |    |

| Notices                                                                       |    |

#### Introduction

**Reliability** generally refers to the infrequency of system and component failures experienced by a server.

**Availability**, broadly speaking, is how the hardware, firmware, operating systems and application designs handle failures to minimize application outages.

**Serviceability** generally refers to the ability to efficiently and effectively install and upgrade systems firmware and applications, as well as to diagnose problems and efficiently repair faulty components when required.

These interrelated concepts of reliability, availability and serviceability are often spoken of as" RAS".

Within a server environment all of RAS, but especially application availability, is really an end-to-end proposition. Attention to RAS needs to permeate all the aspects of application deployment. However, a good foundation for server reliability whether in a scale-out or scale-up environment is clearly beneficial.

Systems based on the Power processors are generally known for their design emphasizing Reliability, Availability and Serviceability capabilities. Previous versions of a RAS whitepaper have been published to discuss general aspects of the hardware reliability and the hardware and firmware aspects of availability and serviceability.

The focus of this whitepaper is to introduce the Power10 processor-based systems using the PowerVM hypervisor. Systems not using PowerVM will not be discussed specifically in this whitepaper.

This whitepaper is organized into five sections:

Section 1: RAS Overview of key Power10 processor-based systems An overview of the RAS capabilities of the latest Power10 processor-based systems.

Section 2: General Design Philosophy

A general discussion of Power RAS design philosophy, priorities, and advantages.

Section 3: Power10 Subsystems RAS Details

A more detailed discussion of each sub-system within a Power server concentrating on the RAS features of processors, memory, and other components of each system.

Section 4: Reliability and Availability in the Data Center

Discussion of RAS measurements and expectations, including various ways in which RAS may be described for systems: Mean Time Between Failures, '9's of availability and so forth.

Section 5: Serviceability

Provides descriptions of the error log analysis, call-home capabilities, service environment and service interfaces.

## Section 1: Overview of Power10 Processor-based systems

### **Comparative Discussion**

In September 2021, IBM introduced the first models using Power10 processors: The IBM Power E1080; a scalable server using multiple four socket Central Electronics Complex (CEC) drawers. The Power E1080 design was inspired by the Power E980 but has enhancements in key areas to complement the performance capabilities of the Power10 processor.

One of these key enhancements includes an all-new memory subsystem with Differential DIMMs (DDIMMs) using a memory buffer that connects to processors using an Open Memory Interface (OMI) which is a serial interface capable of higher speeds with fewer lanes compared to a traditional parallel approach.

Another enhancement is the use of both passive external and internal cables for the fabric busses used to connect processors between drawers eliminating the routing of signals through the CEC backplane in contrast to the Power9 approach where signals were routed through a backplane and the external cables were active. This design point significantly reduces the likelihood that the labor intensive and costly replacement of the main system backplane will be needed. Another change of note from a reliability standpoint is that the processor clock design, while still redundant in the Power E1080 has been simplified since it is no longer required that each processor module within a CEC drawer be synchronized with the others.

Figure 1: Power9/Power10 Servers RAS Highlights Comparison

|                                                                                                                                                                                                                                                         | Power9<br>1s and 2s<br>Systems^ | Power9<br>IBM Power<br>E950 | Power9<br>IBM Power E980 | Power10<br>IBM Power E1080                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Base Power9 <sup>TM</sup> Processor RAS features including  First Failure Data Capture  Processor Instruction Retry  L2/L3 Cache ECC protection with cache linedelete  Power/cooling monitor function integrated into on chip controllers of processors | Yes*                            | Yes                         | Yes                      | Yes                                                                                                                                          |

| Power9 Enterprise RAS Features                                                                                                                                                                                                                          | No                              | Yes                         | Yes                      | Yes                                                                                                                                          |

| Multi-node SMP Fabric RAS  CRC checked processor fabric bus retry with spare data lane and/or bandwidth reduction                                                                                                                                       | N/A                             | N/A                         | Yes                      | Yes – Power10<br>design removes<br>active components<br>on cable and<br>introduces internal<br>cables to reduce<br>backplane<br>replacements |

| PCIe hot-plug with processor integrated PCIe controller <sup>\$</sup>                                                                                                                                                                                   | Yes                             | Yes                         | Yes                      | Yes                                                                                                                                          |

| Memory DIMM ECC supporting x4 Chipkill*                                                                                                                                                                                                                 | Yes                             | Yes                         | Yes                      | Yes                                                                                                                                          |

| Uses IBM memory buffer and has spare DRAM module capability with x4 DIMMs*                                                  | No  | Yes           | Yes                      | Yes – New<br>Memory Buffer                                                            |

|-----------------------------------------------------------------------------------------------------------------------------|-----|---------------|--------------------------|---------------------------------------------------------------------------------------|

| x8 DIMM support with Chipkill correction for marked DRAM*                                                                   | N/A | N/A           | Yes                      | N/A                                                                                   |

| Custom DIMM support with additional spare DRAM capability*                                                                  | No  | No            | Yes                      | Yes, New Custom<br>DIMM                                                               |

| Active Memory Mirroring for the Hypervisor                                                                                  | No  | Yes - Feature | Yes - Base               | Yes- Base                                                                             |

| Redundant/spare voltage phases on voltage converters for levels feeding processor and custom memory DIMMs or memory risers. | No  | Redundant     | Both redundant and spare | Yes, For Processors- DDIMMs use on board power management integrated Circuits (PMICs) |

| Redundant processor clocks                                                                                                  | No  | No            | Yes                      | Yes – New Design                                                                      |

| Redundant service processor and related boot facilities                                                                     | No  | No            | Yes                      | Yes                                                                                   |

| Redundant TPM capability                                                                                                    | No  | No            | Yes                      | Yes                                                                                   |

| Transparent Memory Encryption                                                                                               | No  | No            | No                       | Yes                                                                                   |

| Multi-node support                                                                                                          | No  | No            | Yes                      | Yes                                                                                   |

<sup>\*</sup> In scale-out systems Chipkill capability is per rank of a single Industry Standard DIMM (ISDIMM); in IBM Power E950 Chipkill and spare capability is per rank spanning across an ISDIMM pair; and in the IBM Power E980, per rank spanning across two ports on a Custom DIMM.

The Power E950 also supports DRAM row repair

^ IBM Power® S914, IBM Power® S922, IBM Power® S924

IBM Power® H922, IBM Power® S924, IBM Power® H924

\$Note: I/O adapter and device concurrent maintenance in this document refers to the hardware capability to allow the adapter or device to be removed and replaced concurrent with system operation. Support from the operating system is required and will depend on the adapter or device and configuration deployed.

In July 2022, the General Availability of the Power10 4-Socket enterprise mid-range server and the 1- and 2-sockets scaleout servers followed the GA of the E1080. The table below provide comparison highlights among the current Power10 based systems.

Figure 2: Power10 Servers RAS Highlights Comparison

|                                                                                                                                                                                                                                                                  | Power10<br>1s and 2s<br>IBM Power S1014,<br>S1022, S1024                                                       | Power10<br>IBM Power E1050                                                       | Power10<br>IBM Power E1080                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Base Power10 <sup>TM</sup> Processor RAS features including  • First Failure Data Capture  • Processor Instruction Retry  • L2/L3 Cache ECC protection with cache linedelete  • Power/cooling monitor function integrated into on chip controllers of processors | Yes                                                                                                            | Yes                                                                              | Yes                                                                                                                                    |

| Power10 Enterprise RAS Features • Core Checkstops                                                                                                                                                                                                                | Yes                                                                                                            | Yes                                                                              | Yes                                                                                                                                    |

| <ul> <li>Multi-node SMP Fabric RAS</li> <li>CRC checked processor fabric bus retry with spare data lane and/or bandwidth reduction</li> </ul>                                                                                                                    | N/A                                                                                                            | N/A                                                                              | Yes – Power10 design<br>removes active<br>components on cable and<br>introduces internal cables<br>to reduce backplane<br>replacements |

| PCIe hot-plug with processor integrated PCIe controller                                                                                                                                                                                                          | Yes<br>No Cassette                                                                                             | Yes – with blindswap cassette                                                    | Yes – with blindswap cassette                                                                                                          |

| Memory DIMM ECC supporting x4 Chipkill*                                                                                                                                                                                                                          | Yes                                                                                                            | Yes                                                                              | Yes                                                                                                                                    |

| Dynamic Memory Row repair and spare DRAM capability                                                                                                                                                                                                              | 2U DDIMM – no<br>spare DRAM<br>4U DDIMM (post<br>GA) – 2 spare DRAM<br>per rank<br>Yes – Dynamic Row<br>Repair | Yes - base<br>4U DDIMM – 2 spare<br>DRAM per rank<br>Yes – Dynamic Row<br>Repair | Yes - base<br>4U DDIMM – 2 spare<br>DRAM per rank<br>Yes – Dynamic Row<br>Repair                                                       |

| Active Memory Mirroring for the Hypervisor                                                                                                                                                                                                                       | Yes – Base<br>New to scaleout                                                                                  | Yes - Base                                                                       | Yes - Base                                                                                                                             |

| Redundant/spare voltage phases on voltage converters for levels feeding processor                                                                                                                                                                                | No                                                                                                             | Yes<br>N+1                                                                       | Yes<br>N+2                                                                                                                             |

| Redundant On-board Power Management Integrated Circuits (PMIC) memory DDIMMs                                                                                                                                                                                     | No with<br>2U DDIMM<br>Yes – optional 4U<br>DDIMM (post GA)                                                    | Yes - Base<br>4U DDIMM                                                           | Yes - Base<br>4U DDIMM                                                                                                                 |

| Service Processor Type                                           | Enterprise Base Board Management Controller (eBMC) – open standard with Redfish support | Enterprise Base Board<br>Management<br>Controller (eBMC) –<br>open standard with<br>Redfish support | Flexible Service<br>Processor (FSP) – IBM<br>proprietary |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Processor Clocks Redundancy/Sparing                              | No                                                                                      | Integrated Spare (post GA)                                                                          | Redundant                                                |

| Redundant service processor and related boot facilities          | No                                                                                      | No                                                                                                  | Yes                                                      |

| Boot from more than 1 processor socket (redundant FSP advantage) | No                                                                                      | No                                                                                                  | Yes                                                      |

| Redundant TPM capability (dual TPM module in each drawer)        | No                                                                                      | No                                                                                                  | Yes                                                      |

| Transparent Memory Encryption                                    | Yes                                                                                     | Yes                                                                                                 | Yes                                                      |

| Multi-node support                                               | N/A                                                                                     | N/A                                                                                                 | Yes                                                      |

| Concurrent Op-Panel Repair                                       | No – Op Panel Base<br>Yes - LCD                                                         | Yes – Op Panel Base<br>Yes – LCD<br>(post GA)                                                       | Yes – Op Panel Base<br>Yes - LCD                         |

| TOD Battery Concurrent Maintenance                               | No                                                                                      | Yes                                                                                                 | Yes                                                      |

| Internal Cables                                                  | Lots of internal cables                                                                 | Very Few internal cables                                                                            | Few internal cables                                      |

#### IBM Power E1080

As announced, the Power E1080 is designed to be capable of supporting multiple drawers each containing 4 processor sockets. The initial product offering will be limited to two drawers. In addition to these CEC drawers, the design supports a system control drawer which contains the global service processor modules. Each CEC drawer supports 8 PCIe slots and I/O expansion drawers are also supported.

#### System Structure

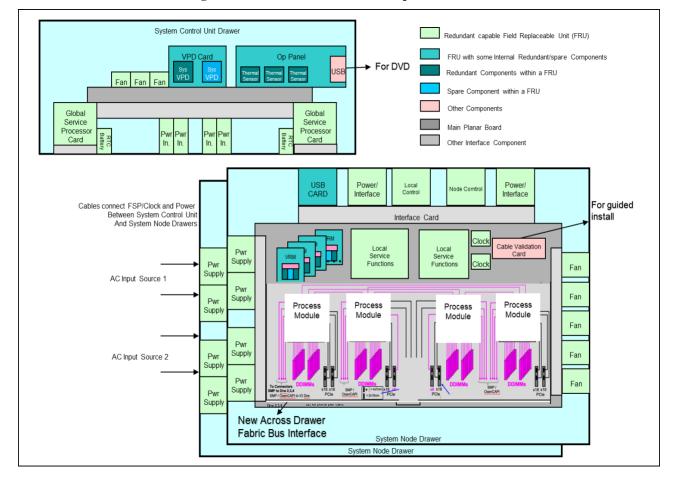

A rough view of the Power E1080 design is represented in the figure below: Compared to the Power E980 the most visible changes are in the memory sub-system and the fabric busses that connect the processors.

Figure 3: Power E1080 Structure Simplified View

Not illustrated in the figure above is the internal connections for the SMP fabric busses which will be discussed in detail in another section.

In comparing the Power E1080 design to the Power9-based Power E980, it is also interesting to note that the processor clock function has been separated from the local service functions and now resides in a dual fashion as separate clock cards.

The Power8 multi-drawer system design required that all processor modules be synchronized across all CEC drawers. Hence a redundant clock card was present in the system control drawer and used for all the processors in the system.

In Power9 only each CEC drawer was required to be synchronized using the same reference clock source. In the Power E1080, each processor can run asynchronous to all the other processors and use a separate/different reference clock source. While a clock and redundant clock is provided in each node (rather than for each processor) there is no need for logic to keep them coordinated. This allows for a significantly simpler clock design.

#### **Power E1080 Processor RAS**

While there are many differences internally in the Power10 processor compared to Power9 that relate to performance, number of cores and so forth, the general RAS philosophy for how errors are handled has remained largely the same.

Two items which have been changed are the memory controller function and the SMP connections between the processors. These will be discussed in the next two sub-sections. The processor clocking has also changed as previously discussed.

### Power E1080 Memory Subsystem

DDIMM NOTE: The diagram shows 1 rank of DRAMs only CRC retry on DDIMM Dynamic row repair Half Bandwidth mode using only 4 lanes 8x Lanes DRAM Sparing and Chipkill Correction allows up to 3 complete 4x Lanes Redundant temperature Data/DRAM Active Checksums Spare PMIC

**Figure 4: DDIMM Memory Features**

The memory subsystem of the Power E1080 has been completely redesigned to support Differential DIMMs (DDIMMs) with DDR4 memory that leverage a serial interface to communicate between processors and the memory.

A memory DIMM is generally considered to consist of 1 or more "ranks" of memory modules (DRAMs). A standard DDIMM module may consist of 1 or 2 ranks of memory and will be approximately 2 standard "rack units" high, called 2U DDIMM. The Power E1080 exclusively uses a larger DDIMM with up to 4 ranks per DDIMM (called a 4U DDIMM). This allows for not

only additional system capacity but also room for additional RAS features to better handle failures on a DDIMM without needing to take a repair action (additional self-healing features). The components of the memory interface include the memory controller on the processors, the open memory interface (OMI) that a memory controller uses to communicate with the memory buffer on each DIMM, the DRAM modules that support a robust error detection and correction capability (ECC), the on-DIMM power management integrated circuits (PMICs) and thermal monitoring capabilities.

These components are considered below looking first at what is standard for both 2U and 4U DDIMMs and then what is unique for the 4U DDIMMs the Power E1080s use.

### Buffer

The DDIMM incorporates a new Microchip memory buffer designed to IBM's RAS specifications. Key RAS features of the buffer include protection of critical data/address flows using CRC, ECC and parity, a maintenance engine for background memory scrubbing and memory diagnostics, and a Fault Isolation Register (FIR) structure which enables firmware attention-based fault isolation and diagnostics.

Unlike Power9 systems, this memory buffer does not contain an L4 cache.

#### **OMI**

The OMI interface between the memory buffer and processor memory controller is protected by CRC retry/recovery facility to re-transmit lost frames to survive intermittent bit flips. A complete lane fail can also be survived by triggering a dynamic lane reduction from 8 to 4, independently for both up and downstream directions. A key advantage of the OMI interface is that it simplifies the number of critical signals that must cross connectors from processor to memory compared to a typical industry standard DIMM design.

### **Memory ECC**

The DDIMM includes a robust 64-byte Memory ECC, with 8-bit symbols, capable of correcting up to five symbol errors (one x4 chip and one additional symbol), as well as retry for data and address uncorrectable errors.

### Dynamic Row Repair

To further extend the life of the DDIMM, the dynamic row repair feature can restore full use of a DRAM for a fault contained to a DRAM row, while system continues to operate.

#### Spare Temperature Sensors

Each DDIMM provides spare temperature sensors, such that the failure of one does not require a DDIMM replacement.

### Unique to 4U DDIMM: Spare DRAMs

4U DDIMMs used in the Power E1080 include two spare x4 memory modules (DRAMs) per rank. These can be substituted for failed DRAMs during runtime operation. Combined with ECC correction, the 2 spares allow the 4U DDIMM to continue to function with 3 bad DRAMs per rank, compared to 1 (single device data correct) or 2 (double device data correct) bad DRAMs in a typical industry standard DIMM design.

This extends self-healing capabilities beyond what is provided with dynamic row repair capability.

#### **Power Management**

In the Power E980, voltage regulator modules (VRMs) in the CEC drawers were separately used to provide different voltage levels to the CDIMMs where the levels would be used or further divided on the CDIMM.

The DDIMMs used in the Power E1080 use power management ICs (PMICs) to divide voltages and provide the power management for the DDIMMs. Separate memory VRMs are no longer used.

The 4U DDIMMs also include spare power management ICs (PMICs) such that the failure of one PMIC does not require a DDIMM replacement.

#### **Power E1080 SMP Interconnections**

### Power E1080 Processor to Processor SMP Fabric Interconnect Within a CEC Drawer

To communicate between processors within a CEC drawer, the Power E1080 uses a fabric bus composed of eight bi-directional lanes of data. The physical busses are run from processor to processor through the CEC drawer main backplane.

The data transferred is CRC checked. Intermittent errors can result in retry of operation. During run-time should a persistent error occur on a bus, the system can reduce from using eight lanes to four lanes. This capability is called "½ bandwidth mode".

### Power E1080 CEC Drawer to CEC Drawer SMP Fabric Interconnect Design

The SMP Fabric busses used to connect processors across CEC nodes is similar in RAS function to the fabric bus used between processors within a CEC drawer. Each bus is functionally composed of eight bi-directional lanes of data. CRC checking with retry is also used. ½ bandwidth mode is supported.

Unlike the processor-to-processor within a node design, the lanes of data are carried from each processor module through internal cables to external cables and then back through internal cables to the other processor.

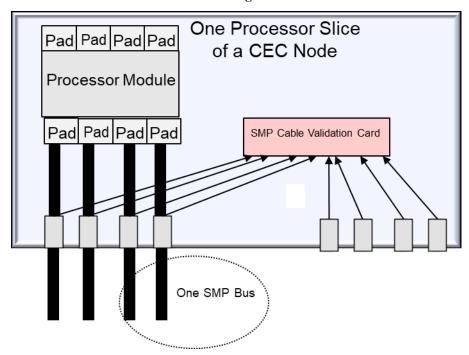

Physically each processor module has eight pads (four on each side of the module.) Each pad side has an internal SMP cable bundle which connects from the processor pads to a bulkhead in each CEC drawer which allows the external and internal SMP cables to be connected to each other.

Figure 5: SMP Fabric Bus Slice

Where the illustration above shows just the connections on one side of the processor. In addition to connecting with the bulkhead, each cable bundle also has connections to an SMP cable Validation Card which has logic used to verify the presence and type of a cable to help guide the installation of cables in a system.

Since physical cables are used, each bus also employs a spare data lane. This can be used to substitute for a failed lane without the need to enter ½ bandwidth mode or the need to schedule a repair.

The ability to concurrently repair an external cable that failed during run-time before a system is rebooted is also supported.

One key difference in this design compared to SMP9 is that the external SMP cable is no longer an active cable. This can be an advantage in reducing the number of components that can fail on the cable, but it does make it harder to isolate the root cause of a cable fault.

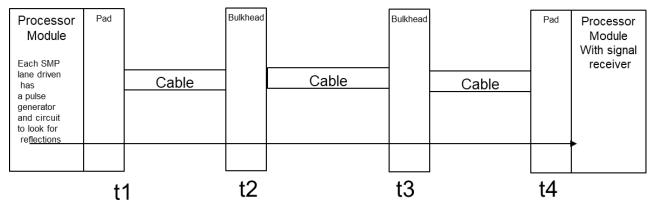

To maintain error isolation with the new cost-effective design, an advanced diagnostic capability called Time Domain Reflectometry (TDR) is built into the Power10 processor and a test performed whenever a bus goes into half-bandwidth mode.

Figure 6: Time Domain Reflectometry

Though it is beyond the scope of this whitepaper to delve into the exact details of how TDR works, as a very rough analogy it can be likened to a form of sonar where when desired, a processor module that drives a signal on a lane can generate an electrical pulse along the path to a receiving processor in another CEC drawer. If there is a fault along the path, the driving processor can detect a kind of echo or reflection of the pulse. The time it takes for the reflection to be received would be indicative of where the fault is within the cable path. For faults that occur mid-cable, the timing is such that TDR should be able to determine exactly what field replaceable unit to replace to fix the problem. If the echo is very close to a connection, two FRUs might be called out, but in any case, the use of TDR allows for good fault isolation for such errors while allowing the Power10 server to take advantage of a fully passive path between processors.

### Power E1080 SMP Fabric Interconnect Design within a CEC Drawer

Unlike the SMP fabric busses between processor drawers, the connections between processors are still routed processor-to-processor within the drawer "planar" or motherboard card instead of cables. The design maintains a CRC checking with retry and the ability to go into a ½ bandwidth mode if needed.

#### **Internal I/O**

The Power E1080 supports 8 PCIe Gen4/Gen5 PCIe slots in each CEC drawer. Up to 4 optional NVMe drives are supported. USB support for the System Control Unit, if desired can be provided by using a USB adapter in one of the 8 PCIe slots and a USB cable connected to the System Control Drawer.

To determine the exact processor to slot assignments, refer to the system documentation or "redbook" for the Power E1080.

Note, however that location codes have been changed for the CEC drawers. Power9 used location codes that began with 1, e.g., P1-C1 would refer to the first planar in a unit and the first connector. In Power10, location codes used to identify elements within the system now begin with a zero., e.g., P0-C0 would be the first planar, first connector.

### Power E1080 and E980 Telemetry Data

These models are designed with extensive thermal and power management capabilities. The E980 and E1080 Power Management unit consists of dedicated controllers that dynamically optimize processor frequency based on the workload. The firmware also has additional monitoring features for memory, IO adapters, system planars, etc. For instance, if a DIMM is running at high temperature, the energy monitoring firmware will detect the event and throttle the memory bandwidth to protect the DIMM.

With the release of HMC1040, the Hardware Management Console (HMC) provides API for customers to acquire power usage and thermal metric from Flexible Service Processor (FSP) based systems. The HMC API return raw, processed, or aggregated power and thermal data. Clients now have the ability to easily gather telemetry data and monitor clusters of E1080 and E980 servers in a datacenter. For more details on the FSP based system telemetry data collection, go to the <a href="IBM Power10 Energy Monitoring">IBM Power10 Energy Monitoring</a> page.

#### **IBM Power E1050**

The Power E1050 is designed to support 2-socket, 3-socket and 4-socket processor configurations. The 2-socket system can be upgraded to 3-socket or 4-socket in the field or at the customer site. Each processor socket is a Dual Chip Module (DCM), which consists of 2 Power10 processor chips. A DCM connects to 16 memory channels, which equates to 64 DDIMMs per fully populated E1050.

As with the E1080, the E1050 customers will benefit from the highly reliable 4U DDIMM. With advanced memory RAS features like integrated spare PMIC, the ability to withstand multiple serial Chipkill events, dynamic DRAM row repair and OMI channel half bandwidth mode, the 4U DDIMM offers in-memory databases very high application availability.

The E1050 introduces the Enterprise Baseboard Controller (eBMC) as the service processor. This is a departure from the IBM proprietary FSP which is used in the E1080 and previous IBM Power enterprise servers. The E1050 eBMC design essentially brings the unmatched enterprise RAS features of the FSP architecture to the industry standard BMC. The eBMC supports the Redfish API which is an open standard designed for simple and secure management of hybrid cloud infrastructure. This allows the E1050 to be easily integrated into any hybrid cloud environment with simplified system serviceability.

The E1050 brings a significantly higher performing machine to the same form factor as the E950 while maintaining the best-in-class RAS. There are more processor cores per die, faster processor interconnect, higher memory bandwidth, more PCIe Gen4/5 slots, to name but a few. These components are protected by CRC and/or ECC with retry capability where appropriate. The use of infrastructure redundancy and concurrent maintenance or hotplug is designed in critical components.

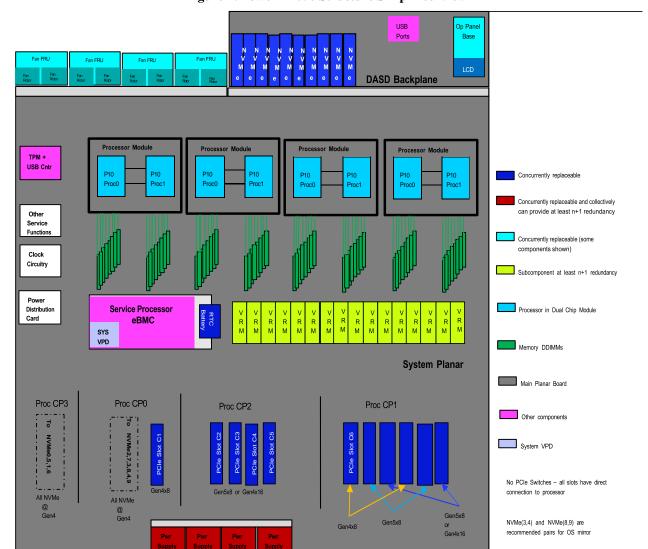

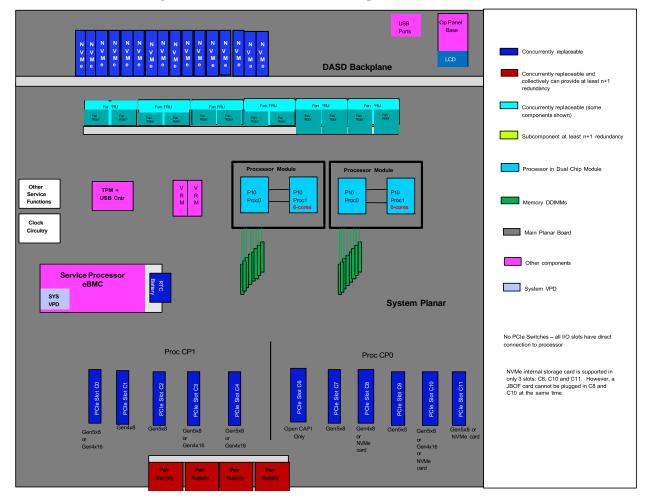

#### System Structure

A simplified view of the Power E1050 design is represented in the figure below: The E1050 maintains the same system form factor and infrastructure redundancy as the E950. As depicted in the E1050 server diagram below, there are 4 Power Supplies and Fan Field Replaceable Units (FRU) to provide at least N+1 redundancy. These components can be concurrently maintained or hot add/removed. There is also N+1 Voltage Regulation Module (VRM) phase redundancy to the Processors and redundant Power Management Integrated Circuit (PMIC) supplying voltage to the 4U DDIMM that the E1050 offers.

The E1050 Op Panel base and LCD are connected to the same planer as the internal NVMe drives. The Op Panel base and LCD are separate FRUs and are concurrently maintainable. The NVMe backplane also has 2 USB 3.0 ports, accessible through the front of the system, for system OS. Not shown in the diagram, are 2 additional OS USB 3.0 ports at the rear of the system, connected through the eBMC card.

Figure 7: Power E1050 Structure Simplified View

#### Power E1050 Processor RAS

The E1050 processor module is a DCM which differs from that of the E950 which has Single Chip Module (SCM). Each DCM has 30 processor cores, which is 120 cores for a 4S E1050 system. In comparison, a 4S E950 server supports 48 cores. The internal processor buses are twice as fast with the E1050 running at 32Gbs. Despite the increased cores and the faster high speed processor bus interfaces, the RAS capabilities are essentially equivalent. With features like Processor Instruction Retry (PIR), L2/L3 Cache ECC protection with cacheline delete and CRC fabric bus retry that is a characteristic of P9 and P10 processors. As in the E950, when an internal or external fabric bus lane encounters a hard failure, the lane can be dynamically spared out with no impact to system availability.

#### Power E1050 Memory RAS

Unlike the processor RAS characteristics, the E1050 memory RAS varies significantly from that of the E950. The E1050 supports the same 4U DDIMM as the E1080.

The memory comparison DIMM table below highlights the differences between the E950 DIMM and the E1050 DDIMM. It also provides the RAS impacts of the DDIMMs, which are applicable to the E1080 servers. For more description on the DDIMM, refer to the E1080 System Memory section of this document.

Figure 8: E950 DIMM vs E1050 DDIMM RAS Comparison

|                                  | Power9<br>E950 Memory                                  | Power10<br>E1050 Memory    | RAS impact                                                                                                                                                                                                                                                                                                                  |

|----------------------------------|--------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIMM Form Factor                 | Riser card plus<br>ISDIMMs                             | 4U DDIMM                   | <ul> <li>P10 4U DDIMM: Single FRU or fewer components to replace</li> <li>E950 DIMM: Separate FRU used for memory buffer on riser card and the ISDIMMs</li> </ul>                                                                                                                                                           |

| symbol Correction                | Single Symbol correction                               | Dual Symbol correction     | <ul> <li>P10 4U DDIMM: Data pin fail (1 symbol) lining up with single cell fail on another DRAM is still correctable</li> <li>E950 DIMM: Data pin fail (1 symbol) lining up with single cell fail on another DRAM is uncorrectable</li> </ul>                                                                               |

| X4 Chip Kill                     | One spare<br>DRAM per<br>port or across a<br>DIMM pair | Two spare<br>DRAM per port | P10 4U DDIMM  1st chip kill fixed with spare  2nd serial chip kill fixed with spare  3rd serial chip kill fixed with ECC  4th serial chip kill is uncorrectable  E950 DIMM  1st chip kill fixed with spare  2nd serial chip kill fixed with ECC  3rd serial chip kill fixed with ECC  3rd serial chip kill is uncorrectable |

| DRAM Row Repair                  | Static                                                 | Dynamic                    | <ul> <li>P10 4U DDIMM: Detect, fix, and restore at runtime without system outage</li> <li>E950 DIMM: Detect at runtime, but fix and restore requires system reboot</li> </ul>                                                                                                                                               |

| L4 Cache                         | Yes                                                    | No                         | <ul> <li>P10 4U DDIMM: Avoids L4 cache failure modes</li> <li>E950 DIMM: L4 cache fails contribute to DIMM replacements</li> </ul>                                                                                                                                                                                          |

| Voltage Regulation<br>Redundancy | No                                                     | Yes                        | <ul> <li>P10 4U DDIMM: can survive a voltage regulation component failure</li> <li>E950 DIMM: voltage regulation and associated components are single point of failure</li> </ul>                                                                                                                                           |

NOTE: A memory ECC code is defined by how many bits or symbols (group of bits) it can correct. The Power10 DDIMM memory buffer ECC code organizes the data into 8-bit symbols and each symbol contains the data from one DRAM DQ over 8 DDR beats.

#### Power E1050 I/O RAS

The E1050 provides 11 general purpose PCIe slots that allows for hot plugging of IO adapters. These PCIe slots operate at Gen4 and Gen5 speeds. As shown in the table below, some of the PCIe slots support I/O expansion drawer cable cards.

Unlike the E950, the E1050 location codes start from index 0, as with all Power10 servers. However, slot c0 is not a general purpose PCIe slot and it's reserved for the eBMC Service Processor card.

Another difference between the E950 and the E1050, is that all the E1050 slots are directly connected to a P10 processor. In the E950 some slots are connected to the P9 processor by way of I/O switches.

All 11 general purpose PCIe slots are available if 3S or 4S DCM are populated. In the 2S DCM configuration, only 7 PCIe slots are functional.

| Slot | Type         | From          | Supports                                    |

|------|--------------|---------------|---------------------------------------------|

| C1   | x8 G4        | CP0 = DCM0/C0 | PCIe Adapters, Cable card for I/O expansion |

| C2   | x8 G5/x16 G4 | CP2 = DCM2/C1 | PCIe Adapters, Cable card for I/O expansion |

| C3   | x8 G5/x16 G4 | CP2 = DCM2/C1 | PCIe Adapters, Cable card for I/O expansion |

| C4   | x8 G5/x16 G4 | CP2 = DCM2/C0 | PCIe Adapters, Cable card for I/O expansion |

| C5   | x8 G5/x16 G4 | CP2 = DCM2/C0 | PCIe Adapters, Cable card for I/O expansion |

| C6   | x8 G4        | CP1 = DCM1/C1 | PCIe Adapters                               |

| C7   | x8 G5        | CP1 = DCM1/C1 | PCIe Adapters, Cable card for I/O expansion |

| C8   | x8 G5/x16 G4 | CP1 = DCM1/C1 | PCIe Adapters, Cable card for I/O expansion |

| C9   | x8 G4        | CP1 = DCM1/C0 | PCIe Adapters                               |

| C10  | x8 G5        | CP1 = DCM1/C0 | PCIe Adapters, Cable card for I/O expansion |

| C11  | x8 G5/x16 G4 | CP1 = DCM1/C0 | PCIe Adapters, Cable card for I/O expansion |

Figure 9: Power E1050 I/O Slot Assignments

## **DASD Options**

The E1050 provides 10 internal NVMe drives at Gen4 speeds. The NVMe drives are connected to DCM0 and DCM3. In a 2S DCM configuration, only 6 of the drives are available. A 4S DCM configuration is required to have access to all 10 internal NVMe drives. Unlike the E950, the E1050 has no internal SAS drives. An external drawer can be used to provide SAS drives.

The internal NVMe drives support OS-controlled RAID0 and RAID1 array, but no hardware RAID. For best redundancy, the OS mirror and dual VIOS mirror can be employed. To ensure as much separation as possible in the hardware path between mirror pairs, the following NVMe configuration is recommended:

- a.) Mirrored OS: NVMe3,4 or NVME8,9 pairs

- b.) Mirrored Dual VIOS

- I. Dual VIOS: NVMe3 for VIOS1, NVMe4 for VIOS2

- II. Mirrored the Dual VIOS: NVMe9 mirrors NVMe3, NVMe8 mirrors NVMe4

#### Power E1050 Service Processor

The IBM Power10 E1050 comes with a redesigned service processor based on a Baseboard Management Controller (BMC) design with firmware that is accessible through open-source industry standard APIs, such as Redfish. An upgraded Advanced System Management Interface

(ASMI) web browser user interface preserves the required enterprise RAS functions while allowing the user to perform tasks in a more intuitive way.

Equipping the industry standard BMC with enterprise service processor functions that are characteristic of FSP based systems, like the E1080, has led to the name Enterprise BMC (eBMC). As with the FSP, the eBMC runs on its own power boundary and does not require resources from a system processor to be operational to perform its tasks.

The service processor supports surveillance of the connection to the Hardware Management Console (HMC) and to the system firmware (hypervisor). It also provides several remote power control options, environmental monitoring, reset, restart, remote maintenance, and diagnostic functions, including console mirroring. The BMC service processors menus (ASMI) can be accessed concurrently during system operation, allowing nondisruptive abilities to change system default parameters, view and download error logs, check system health.

Redfish, an Industry standard for server management, enables the Power Servers to be managed individually or in a large data center. Standard functions such as inventory, event logs, sensors, dumps, and certificate management are all supported with Redfish. In addition, new user management features support multiple users and privileges on the BMC via Redfish or ASMI. User management via Lightweight Directory Access Protocol (LDAP) is also supported. The Redfish events service provides a means for notification of specific critical events such that actions can be taken to correct issues. The Redfish telemetry service provides access to a wide variety of data (e.g. power consumption, ambient, core, DDIMM and I/O temperatures, etc.) that can be streamed on periodic intervals.

### **IBM Power S1014, S1022, S1024 Servers**

The Power S1014, S1022 and S1024 are the Power10 Scaled out servers. These systems are offered in the 1S and 2S DCM configuration with 2U and 4U CEC drawer options.

## System Structure

There are multiple scale out system models (MTMs) supported. For brevity, this document focuses on the largest configuration of the scale out servers.

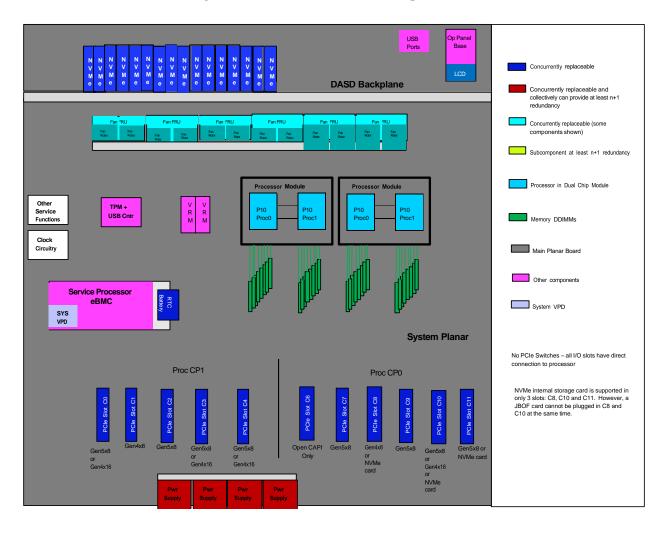

The simplified illustration, in Figure 10, depicts the 2S DCM with 4U CEC drawer. Similar to the S9xx, there is infrastructure redundancy in the power supplies and fans. In addition, these components can be concurrently maintained along with the Op Panel LCD, internal NVMe drives and IO adapters.

Figure 10: Power S1024 Structure Simplified View

As depicted in the simplified illustration in Figure 11, there is another variation of the Power10 processor module. This option contains 1 P10 chip with processor cores and OMI memory channels and another P10 chip whose primary purpose is to provide PCIe connections to I/O devices. This P10 entry Single Chip Module (eSCM) processor configuration gives customers the option to purchase cost reduced solution without losing any I/O adapter slots. A point of note is if the primary processor chip of the eSCM is nonfunctional and garded by the firmware, the

associated I/O only chip will be deconfigured as well and all the attached I/O slots will be unavailable.

Figure 11: Power S1024 Structure Simplified View With eSCM

## Power S1014, S1022, S1024 Processor and Memory RAS

Other than the differences between the eSCM, DCM and SCM configurations outlined above, the processor RAS for these systems will be similar to enterprise systems. Refer to the E1050 processor RAS section and the general Power10 RAS comparison tables for more details.

The memory on these systems is very different from that of the S9xx systems. These scale out systems now support Active Memory Mirroring for the Hypervisor, which was not available in the S9xx servers. While an S9xx uses ISDIMMs, these systems support a 2U DDIMM which is a DDIMM form-factor that fits in 2U systems. The 2U DDIMM is a reduced cost and RAS

version of the 4U DDIMM. The 4U DDIMMs RAS characteristics were discussed in some details in the E1080 section of this document.

Figure 12: S9xx ISDIMM vs 2U DDIMM RAS Comparison

|                                  | Power9<br>S9xx Memory                                       | Power10<br>S1014, S1022,<br>S1024<br>2U Memory     | RAS impact                                                                                                                                                                                                                                                            |

|----------------------------------|-------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIMM Form Factor                 | Direct attached ISDIMMs                                     | 2U                                                 | <ul> <li>P10 2U DDIMM: Single FRU or fewer components to replace</li> <li>S9xx DIMM: Separate FRU used for the ISDIMMs</li> </ul>                                                                                                                                     |

| Symbol Correction                | Dual Symbol correction                                      | Dual Symbol correction                             | <ul> <li>P10 2U DDIMM: Data pin fail (1 symbol) lining up with single cell fail on another DRAM is still correctable</li> <li>S9xx DIMM: Data pin fail (1 symbol) lining up with single cell fail on another DRAM is still correctable</li> </ul>                     |

| X4 Chip Kill                     | Single DRAM<br>chipkill correction,<br>but No spare<br>DRAM | Single DRAM chipkill correction, but No spare DRAM | <ul> <li>P10 2U DDIMM         <ul> <li>1st chip kill fixed with ECC</li> <li>2nd serial chip kill is uncorrectable</li> </ul> </li> <li>S9xx DIMM         <ul> <li>1st chip kill fixed with ECC</li> <li>2nd serial chip kill is uncorrectable</li> </ul> </li> </ul> |

| DRAM Row Repair                  | No                                                          | Dynamic                                            | <ul> <li>P10 2U DDIMM: Detect, fix, and restore at runtime without system outage</li> <li>S9xx ISDIMM: Neither Static nor Dynamic row repair supported</li> </ul>                                                                                                     |

| Voltage Regulation<br>Redundancy | No                                                          | No                                                 | <ul> <li>P10 2U DDIMM: voltage regulation and associated components are single point of failure</li> <li>S9xx DIMM: voltage regulation and associated components are single point of failure</li> </ul>                                                               |

NOTE: A memory ECC code is defined by how many bits or symbols (group of bits) it can correct. The P10 DDIMM memory buffer ECC code organizes the data into 8-bit symbols and each symbol contains the data from one DRAM DQ over 8 DDR beats.

#### Power S1014, S1022, S1024 I/O RAS

The S1024 provides 10 general purpose PCIe slots that allows for hot plugging of IO adapters. Some of these PCIe slots operate at Gen5 speeds, while a few are limited to Gen4 speeds. As shown in Figure 13, some of the PCIe slots support NVMe JBOF (Just a Bunch Of Flash) cable card and I/O expansion drawer cable card.

Both DCMs must be installed to have connection to all 10 PCIe I/O slots. If only one DCM is installed, the 1S processor module drives 5 general purpose PCIe slots (C7 to C11).

Figure 13: Power S1024 I/O Slot Assignments

| Slot | Туре         | From          | Supports                                               |

|------|--------------|---------------|--------------------------------------------------------|

| C0   | x8 G5/x16 G4 | CP1 = DCM1/C1 | PCIe Adapters, Cable card for I/O expansion            |

| C1   | x8 G4        | CP1 = DCM1/C1 | PCIe Adapters                                          |

| C2   | x8 G5        | CP1 = DCM1/C1 | PCIe Adapters, Cable card for I/O expansion            |

| C3   | x8 G5/x16 G4 | CP1 = DCM1/C0 | PCIe Adapters, Cable card for I/O expansion            |

| C4   | x8 G5/x16 G4 | CP1 = DCM1/C0 | PCIe Adapters, Cable card for I/O expansion            |

| C7   | x8 G5        | CP0 = DCM0/C1 | PCIe Adapters, Cable card for I/O expansion            |

| C8   | x8 G4        | CP0 = DCM0/C1 | PCIe Adapters, NVMe JBOF card                          |

| C9   | x8 G5        | CP0 = DCM0/C1 | PCIe Adapters, Cable card for I/O expansion            |

| C10  | x8 G5/x16 G4 | CP0 = DCM0/C0 | PCIe Adapters, Cable card for I/O expansion, NVMe JBOF |

| C11  | x8 G5        | CP0 = DCM0/C0 | PCIe Adapters, Cable card for I/O expansion, NVMe JBOF |

### DASD Options

These systems provide up to 16 internal NVMe drives at Gen4 speeds. The NVMe drives are connected to the processor via a plug-in PCIe NVMe JBOF (Just a Bunch Of Flash) card. Up to 2 JBOF cards can be populated in the S1024 and S1014 servers, with each JBOF card attached to an 8-pack NVMe backplane. The S1022 NVMe backplane only supports the 4-pack, which provides up to 8 NVMe drive per system. The JBOF cards are operational in PCIe slots C8, C10 and C11 only. However, the C8 and C10 slots cannot both be populated with JBOF cards simultaneously. As depicted in Figure 13 above, all 3 slots are connected to DCM0 which means a 1S system can have all the internal NVMe drives available. While the NVMe drives are concurrently maintainable, a JBOF card is not. Unlike the S9xx, these systems have no internal SAS drives. An external drawer can be used to provide SAS drives.

### Power S1014, S1022, S1024 Service Processor

These systems use the same eBMC service processor as the E1050 servers. Refer to the Power E1050 Service Processor section of this document for more information.

#### **IBM Power S1012**

In May of 2024, IBM announced another Power10 processor-based system, The IBM Power S1012.

The S1012 is described as an edge-level server, designed for both edge computing and core business workloads. The edge-level server is a 1-socket half-wide system available in a 2U rack-mounted or tower chassis form factor.

While the system benefits from incorporating a Power10 processor, an eBMC and many firmware components shared in common with other systems, the system design, positioning and form-factor is different from others in the Power10 family. Consequently, there are a number of RAS characteristics that are different from the other Power10 servers described in this whitepaper.

A brief highlight of some of the key differences follows.

Rather than using 2U DDIMMs, the system supports DDR4 Industry Standard RDIMMs (ISDIMMS). The processor connects to the ISDIMMS through separate memory buffers incorporated on the system planar.

The S1012 does not support Active Memory Mirroring of the Hypervisor and dynamic memory deallocation for predictive memory failure. The PCIe I/O Adapters are not concurrently maintainable and external I/O drawers are not supported. Live Partition Mobility (LPM) is now supported for the Power S1012 with post General Availability (GA) firmware.

The system does support redundancy in system fans and power supplies as well as concurrent maintenance. The four NVMe drives are accessible for hot-plugging (when allowed by the operating system.) The 4 PCIe slots do not support concurrently maintainable or hot-plugging of adapters.

Due to limited number of components in the system, the use of fault indicators for failing part indication is more limiting compared to the scale-out systems.

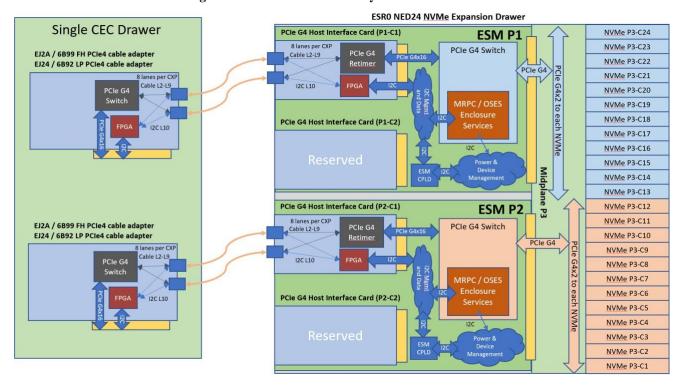

### NVMe Expansion Drawer (NED24)

The PCIe Gen4 NVMe Expansion Drawer can be used in systems to increase storage capacity. The NED24 NVMe expansion drawer provides extra NVMe U.2 drives. It is connected to system units by two expansion drawer cable pairs. The NED24 NVMe expansion drawer can hold up to 24 small form factor (SFF) NVMe U.2 drives. Depending on system model two or more can be attached for capacity or redundancy.

Figure 14: The NED24 I/O Subsystem Structure

The PCIe x16 uplink to the system cable cards is carried over a pair of x16 cables. Connectivity is fault tolerant of either cable of the pair failing and can be repaired independently. The management of the drawer is provided by two Enclosure Services Modules (ESM) with either being capable of managing the drawer.